# 100GBASE-LR4 & OTU4 10km CFP Optical Transceiver GCF-S101-LR4C

#### **Features**

- ✓ Hot-pluggable CFP form factor

- √ 4 channels full-duplex transceiver module

- ✓ Supports 111.8Gb/s aggregate bit rate

- √ 4 channels DFB-based LAN-WDM cooling transmitter

- √ 4 channels PIN ROSA

- √ 9W maximum power dissipation

- ✓ Maximum link length of 10km on SMF

- ✓ Duplex LC receptacle

- ✓ Built-in digital diagnostic functions

- ✓ Operating case temperature range: 0 to 70°C

- ✓ Single 3.3V power supply

- ✓ RoHS-6 compliant (lead free)

#### **Applications**

- √ 100GBASE-LR4 100G Ethernet

- ✓ OTN OTU4 applications

#### **Description**

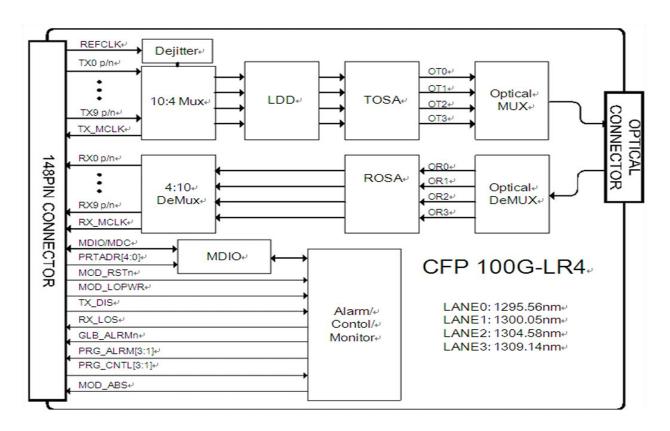

The Gigalight 100GBASE-LR4 & OTU4 10km CFP optical transceiver, 100G CFP LR4/OTU4 (GCF-S101-LR4C) is designed for use in 100-Gigabit Ethernet and OTN links up to 10km on Single Mode Fiber (SMF). It is compliant with the CFP MSA, IEEE 802.3ba 100GBASE-LR4, and OTU4 standards. Digital diagnostics functions are available via an MDIO interface, as specified by the CFP MSA. The module converts 10-lane electrical data streams to 4-lane optical output signal and 4-lane optical input signal to 10-lane electrical data streams. This 10-lane electrical signal is fully compliant with 802.3ba CAUI specification and allows FR4 host PCB trace up to 25cm. The high-performance cooled LAN-WDM EML transmitter and high-sensitivity PIN receiver provide superior performance for 100-Gigabit Ethernet applications up to 10km links.

Figure 1: Module Block Diagram

#### **Absolute Maximum Ratings**

| Parameter                             | Symbol           | Min  | Max | Unit |

|---------------------------------------|------------------|------|-----|------|

| Supply Voltage                        | V <sub>cc</sub>  | -0.5 | 3.6 | V    |

| Storage Temperature                   | Ts               | -40  | 85  | °C   |

| Case Operating Temperature            | Tc               | -5   | 75  | °C   |

| Humidity (non-condensing)             | Rh               | 5    | 85  | %    |

| Receiver Damage Threshold (each lane) | P <sub>dag</sub> | 5.5  |     | dBm  |

#### **Recommended Operating Conditions**

| Parameter                  | Symbol          | Min | Typical | Max   | Unit |

|----------------------------|-----------------|-----|---------|-------|------|

| Supply Voltage             | V <sub>cc</sub> | 3.2 | 3.3     | 3.4   | V    |

| Operating Case Temperature | T <sub>c</sub>  | 0   |         | 70    | °C   |

| Data Rate                  |                 |     | 103.125 | 111.8 | Gb/s |

## **Data Sheet**

**Products Characteristics** (tested under recommended operating conditions)

| Products Character                |                      |           |                      | ·                  |         |                        |

|-----------------------------------|----------------------|-----------|----------------------|--------------------|---------|------------------------|

| Parameter                         | Symbol               |           | Min                  | Typical            | Max     | Notes                  |

|                                   | Voltage S            | upply E   | lectrical C          | haracteristics     |         |                        |

| Supply Current Tx / Rx            | I <sub>cc</sub>      | Α         |                      |                    | 3       | 1                      |

| Power Supply Noise                | V <sub>rip</sub>     |           |                      |                    | 2%      | DC-1MHz                |

| 11.7                              | ·                    |           |                      |                    | 3%      | 1-10MHz                |

| Dissipation Class2                | Pw                   | W         |                      |                    | 9       |                        |

| Low Power Dissipation             | P <sub>low</sub>     | W         |                      |                    | 2       |                        |

| Inrush Current n 2                | I <sub>inrush</sub>  | mA/usec   |                      |                    | 50      |                        |

| Turn-off Current Class2           | I <sub>turnoff</sub> | mA/usec   | -50                  |                    |         |                        |

|                                   | Different :          | Signal E  | lectrical C          | haracteristics     |         |                        |

| Single Ended Data Input Swing     |                      | mV        | 55                   |                    | 525     |                        |

| Single Ended Data Output Swing    |                      | mV        | 180                  |                    | 385     |                        |

| Differential Signal Resistance    | Output               | Ω         | 80                   |                    | 120     |                        |

| Differential Signal Resistance    | Input                | Ω         | 80                   |                    | 120     |                        |

|                                   | 3.3V LVC             | MOS EI    | ectrical Cl          | naracteristics     |         |                        |

| Input High Voltage                | 3.3V <sub>IH</sub>   | V         | 2.0                  |                    | Vcc+0.3 |                        |

| Input Low Voltage                 | 3.3V <sub>IL</sub>   | V         | -0.3                 |                    | 0.8     |                        |

| Input Leakage Current             | 3.31 <sub>IN</sub>   | uA        | -10                  |                    | 10      |                        |

| Output High Voltage               | 3.3V <sub>OH</sub>   | V         | V <sub>cc</sub> -0.2 |                    |         | I <sub>OH</sub> =100uA |

| Output Low Voltage                | 3.3V <sub>OL</sub>   | V         |                      |                    | 0.2     | I <sub>OL</sub> =100uA |

| Pulse Width of Control Pin Signal | T_CNTL               | us        | 100                  |                    |         |                        |

|                                   | 1.2V LVC             | MOS EI    | ectrical Ch          | naracteristics     |         |                        |

| Input High Voltage                | 1.2V <sub>IH</sub>   | V         | 0.84                 |                    | 1.5     |                        |

| Input Low Voltage                 | 1.2V <sub>IL</sub>   | V         | -0.3                 |                    | 0.36    |                        |

| Input Leakage Current             | 1.2I <sub>IN</sub>   | uA        | -100                 |                    | 100     |                        |

| Output High Voltage               | 1.2V <sub>OH</sub>   | V         | 1.0                  |                    | 1.5     |                        |

| Output Low Voltage                | 1.2V <sub>OL</sub>   | V         | -0.3                 |                    | 0.2     |                        |

| Output High Current               | 1.2I <sub>OH</sub>   | mA        |                      |                    | -4      |                        |

| Output Low Current                | 1.2I <sub>OL</sub>   | mA        | 4                    |                    |         |                        |

| Input Capacitance                 | Ci                   | pF        |                      |                    | 10      |                        |

| Op                                | tical Tran           | smitter ( | Character            | istics (each lane) |         |                        |

| Signaling Rate @100GbE            |                      |           |                      | 25.78125+/-100ppm  |         |                        |

| Signaling Rate @OTU4              |                      | Gb/s      |                      | 27.95249+/-20ppm   |         |                        |

|                                   | λ1                   |           | 1294.53              | 1295.56            | 1296.59 |                        |

|                                   | λ2                   |           | 1299.02              | 1300.05            | 1301.09 |                        |

| Wavelength Range                  | λ3                   | nm        | 1303.54              | 1304.58            | 1305.63 |                        |

|                                   | λ4                   |           | 1308.09              | 1309.14            | 1310.19 |                        |

| Side Mode Suppression Ratio       | SMSR                 | dB        | 30                   |                    |         |                        |

| Total Average Laurah Dawa         | Б                    | حال       |                      |                    | 10.5    | @100GbE                |

| Total Average Launch Power        | Pt                   | dBm       |                      |                    | 8.9     | @OTU4                  |

| Average Loureh Dows-2             | В                    | dD:       | -4.3                 |                    | 4. 5    | @100GbE                |

| Average Launch Power <sup>2</sup> | Pa                   | dBm       | -2.5                 |                    | 2.9     | @OTU4                  |

| Optical Modulation Amplitude      | OMA                  | dBm       | -1.3                 |                    | 4.5     | 3                      |

#### Optical Interconnection Design Innovator

| Transmitter and Dispersion                            | TDP              | dB      |               |                        | 2.2     | @100GbE              |

|-------------------------------------------------------|------------------|---------|---------------|------------------------|---------|----------------------|

| Penalty                                               | IDP              | UD      |               |                        | 1.5     | @OTU4                |

| Average Launch Power of Off<br>Transmitter            | P <sub>off</sub> | dBm     |               |                        | -30     |                      |

| Extination Datie                                      | ГР               | 40      | 4             |                        |         | @100GbE              |

| Extinction Ratio                                      | ER               | dB      | 7             |                        |         | @OTU4                |

| Channel Power Difference                              |                  | dB      |               |                        | 5       |                      |

| RIN20 OMA                                             |                  | dB/Hz   |               |                        | -130    |                      |

| Optical Return Loss Tolerance                         | T <sub>RL</sub>  | dB      |               |                        | 20      |                      |

| Transmitter Reflectance                               | R⊤               | dB      |               |                        | -12     | 4                    |

| Eye Diagram                                           |                  | С       | ompliant with | n IEEE 802.3ba-2010/G. | 959.1)  |                      |

| C                                                     | ptical Red       | eiver C | haracteris    | tics (each lane)       |         |                      |

| Receive Rate                                          |                  | Gb/s    |               | 25.78125+/-100ppm      |         | @100GbE              |

| Noocive Nate                                          |                  | Gb/S    |               | 27.95249+/-20ppm       |         | @OTU4                |

|                                                       | λ1               |         | 1294.53       | 1295.56                | 1296.59 |                      |

|                                                       | λ2               |         | 1299.02       | 1300.05                | 1301.09 |                      |

| Four Lane Wavelength Range                            | λ3               | nm      | 1303.54       | 1304.58                | 1305.63 |                      |

|                                                       | λ4               |         | 1308.09       | 1309.14                | 1310.19 |                      |

| Overload Input Optical Power                          | P <sub>max</sub> | dBm     | 4.5           |                        |         | 5                    |

| Total Input Optical Power                             | Pt               | dBm     |               |                        | 8.9     | @OTU4                |

| Average Receive Power <sup>6</sup>                    | Pin              | dBm     | -10.6         |                        | 4.5     | @100GbE              |

| Average Receive Fower                                 | FIII             | ubili   | -8.8          |                        | 2.9     | @OTU4                |

| Receive Power in OMA                                  | PinOMA           | dBm     |               |                        | 4.5     |                      |

| Difference in Receive Power                           |                  | dBm     |               |                        | 5.5     |                      |

| Receiver Sensitivity in OMA                           | Pmin             | dBm     |               |                        | -8.6    | @100GbE <sup>7</sup> |

| receiver censilivity in civil                         | 1 111111         | dbiii   |               |                        | -10.3   | @OTU4 <sup>8</sup>   |

| Stressed Receiver Sensitivity in OMA <sup>9, 10</sup> |                  | dBm     |               |                        | -6.8    |                      |

| Los Assert                                            | LOSA             | dBm     | -20           |                        | -15     |                      |

| Los De-assert                                         | LOS <sub>D</sub> | dBm     |               |                        | -14     |                      |

| Los Hysteresis                                        | LOS <sub>H</sub> | dBm     | 0.5           |                        |         |                      |

| Chromatic Dispersion                                  |                  | Ps/nm   | -28.5         |                        | +9.5    |                      |

| Maximum Reflectance                                   |                  | dB      |               |                        | -26     |                      |

| Delay Group Differential                              |                  | ps      |               |                        | 8       |                      |

#### **Notes:**

- 1. The supply current includes CFP module's supply current and test board working current.

- 2. Each lane (min) is informative and not the principal indicator of signal strength. A transmitter with launch power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 3. Even if the TDP < 1dB, the OMA (min) must exceed this value.

- 4. Defined looking into the transmitter.

### **Data Sheet**

## **Gigalight**Optical Interconnection Design Innovator

- 5. The receiver shall be able to tolerate, without damage, continuous exposure to an optical input signal having this average power level.

- 6. Each lane (max) for 100GBASE-ER4 is larger than the 100BASE-ER4 transmitter value to allow compatibility with 100BASE-LR4 units at short distances. Each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance.

- 7. Each lane (max) is informative.

- 8. Measured with PRBS 2<sup>31</sup>-1 for BER=10<sup>-5</sup>. The BER for the OTU4 application is required to be met only after FEC has been applied.

- 9. Measured with conformance test signal at TP3 for BER=10<sup>-12</sup>

- 10. Conditions of stressed receiver sensitivity test: vertical eye closure penalty for each lane is 1.8dB; stressed eye J2 jitter for each lane is 0.3UI; stressed eye J9 jitter for each lane is 0.47UI.

#### **Hardware Control Pins**

The CFP module supports real-time control functions via hardware pins.

| Pin# | Symbol     | Description                                                                      |   | Logic          | Н            | L      | Pull-up/down <sup>1, 2</sup> |

|------|------------|----------------------------------------------------------------------------------|---|----------------|--------------|--------|------------------------------|

| 30   | PRG_CNTL1  | Programmable Control 1 MSADefault: TRXIC_RST n , TX&RX ICs reset, "0":reset; "1" | I | 3.3V<br>LVCMOS | per CFF      | ) MSA  | Pull-Up                      |

| 31   | PRG_CNTL2  | Programmable Control 2 MSA<br>Default : Hardware Interlock LSB                   |   |                | Pull-Up      |        |                              |

| 32   | PRG_CNTL3  | Programmable Control 3 MSA<br>Default: Hardware Interlock MSB                    | I | 3.3V<br>LVCMOS |              |        | Pull-Up                      |

| 36   | TX_DIS     | Transmitter Disable                                                              | I | 3.3V<br>LVCMOS | Disable      | Enable | Pull-Up                      |

| 37   | MOD_LOPW R | Module Low Power Mode                                                            | ı | 3.3V<br>LVCMOS | Low<br>Power | Enable | Pull-Up                      |

| 39   | MOD_RSTn   | Module Reset (Invert)                                                            | I | 3.3V<br>LVCMOS | Enable       | Reset  | Pull-Down                    |

#### Note:

- 1. Pull-Up resistor (4.7k to 10k Ohm) is located within the CFP module.

- 2. Push-Down resistor (4.7k to 10k Ohm) is located within the CFP module.

# **Optical Transceivers Data Sheet**

#### Optical Interconnection Design Innovator

#### **Hardware Alarm Pins**

The CFP module supports alarm hardware pins.

| Pin# | Symbol     | Description                                                                    |   | Logic          | Н                 | L       | Pull-up/down <sup>1, 2</sup> |

|------|------------|--------------------------------------------------------------------------------|---|----------------|-------------------|---------|------------------------------|

| 33   | prg_alrm1  | Programmable Alarm 1 MSA<br>Default:HIPWR_ON                                   | 0 | 3.3V<br>LVCMOS | Active H          |         |                              |

| 34   | PRG ALRM 2 | Programmable Alarm 2MSA<br>default:MOD_READY , Ready<br>State has been reached | 0 | 3.3V<br>LVCMOS |                   |         |                              |

| 35   | PRG ALRM3  | Programmable Alarm 3<br>MSA Default: MOD FAULT                                 | 0 | 3.3V<br>LVCMOS |                   |         |                              |

| 38   | MOD_ABS    | Module Absent                                                                  | 0 | 3.3V<br>LVCMOS | Absent            | Present | Pull-Down                    |

| 40   | RX_LOS     | Receiver Loss of Signal                                                        | 0 | 3.3V<br>LVCMOS | Loss of<br>Signal | ОК      |                              |

#### Note:

- 1. Pull-Up resistor (4.7k to 10k Ohm) is located within the CFP module.

- 2. Push-Down resistor (4.7k to 10k Ohm) is located within the CFP module.

#### **Management Interface Pins (MDIO)**

The CFP Module supports alarm, control and monitor functions via an MDIO bus.

| Pin# | Symbol                             | Description                  | I/O                                | Logic  | Н      | L         | Pull-up/down |      |  |        |  |  |  |

|------|------------------------------------|------------------------------|------------------------------------|--------|--------|-----------|--------------|------|--|--------|--|--|--|

| 41   | GLB ALRMn                          | Global Alarm                 | ı                                  | 3.3V   | Absent | Alarm     | Pull-Down    |      |  |        |  |  |  |

| 7.   | _                                  |                              |                                    | LVCMOS |        | 7 (101111 |              |      |  |        |  |  |  |

| 47   | MDIO                               | Management Data Input Output | 1/0                                | 1.2V   |        |           |              |      |  |        |  |  |  |

| 47   | WIBTO                              | Bi-Directional Data          | 170                                | LVCMOS |        |           |              |      |  |        |  |  |  |

| 48   | MDC                                | MDIO Clock                   | 1                                  | 1.2V   |        |           |              |      |  |        |  |  |  |

| 40   | WIDO                               | WETE Clock                   | •                                  | LVCMOS |        |           |              |      |  |        |  |  |  |

| 46   | MDIO Physical Port address         |                              | PRTADR0 MDIO Physical Port address | 1      | 1.2V   |           |              |      |  |        |  |  |  |

| 40   |                                    | bit0                         |                                    | bit0   |        | LVCMOS    |              |      |  |        |  |  |  |

| 45   | PRTADR1 MDIO Physical Port addre   |                              | 1                                  | 1.2V   |        |           |              |      |  |        |  |  |  |

| 45   | TRIABILI                           | bit1                         |                                    | bit1   |        | bit1      |              | bit1 |  | LVCMOS |  |  |  |

| 44   | PRTADR2                            | MDIO Physical Port address   | 1                                  | 1.2V   | per M  | IDIO      |              |      |  |        |  |  |  |

| 44   | TRIABILE                           | bit2                         |                                    | LVCMOS | docum  | ent[5]    |              |      |  |        |  |  |  |

| 42   | PRTADR3 MDIO Physical Port address |                              | 1                                  | 1.2V   |        |           |              |      |  |        |  |  |  |

| 43   | TATABLE                            | bit3                         |                                    | LVCMOS |        |           |              |      |  |        |  |  |  |

| 40   | PRTADR4                            | MDIO Physical Port address   | 1                                  | 1.2V   |        |           |              |      |  |        |  |  |  |

| 42   | TRIADIC                            | bit4                         | '                                  | LVCMOS |        |           |              |      |  |        |  |  |  |

### **Data Sheet**

**Hardware Signaling Pin Timing Requirements**

| Parameter                    | Symbol                 | Min | Max | Unit | Notes& Conditions                                                                  |

|------------------------------|------------------------|-----|-----|------|------------------------------------------------------------------------------------|

| Hardware<br>MOD_LOPWR Assert | t_MOD_LOPW<br>R_Assert |     | 1   | ms   | Application specific may depend on current state condition when signal is applied. |

| TX Disable Assert Time       | T_off                  |     | 100 | us   |                                                                                    |

#### **Electrical Characteristics**

#### **Reference Clock Characteristics**

| Parameter                      | Symbol         | Min  | Typical                   | Max  | Unit | Notes                                   |

|--------------------------------|----------------|------|---------------------------|------|------|-----------------------------------------|

| Impedance                      | Z <sub>d</sub> | 80   | 100                       | 120  | Q    |                                         |

| Frequency                      |                |      | 161.1328125/<br>644.53125 |      | MHz  | 1/64 or 1/16 of electrical lane rate    |

| Francisco Ctability            | ∆f             | -100 |                           | 100  | nnm  | For Ethernet applications               |

| Frequency Stability            |                | -20  |                           | 20   | ppm  | For Telecom applications                |

| Output Differential<br>Voltage | $V_{DIFF}$     | 400  |                           | 1200 | mV   | Peak to Peak Differential               |

| RMS Jitter1-2                  | 0              |      |                           | 10   | ne   | Random Jitter Over frequency            |

| RIVIS JILLET 1-2               | Ŭ              |      |                           | 10   | ps   | band of 10KHz <f<10mh< td=""></f<10mh<> |

| Clock Duty Cycle               |                | 40   |                           | 60   | %    |                                         |

| Clock Rise/Fall Time           | tr/f           | 200  |                           | 1250 | ne   | 1/64 of electrical lane rate            |

| 10%/90%                        | 4/1            | 50   |                           | 315  | ps   | 1/16 of electrical lane rate            |

#### Note:

- 1. The term "40GBASE\_FR" is the 40GbE serial optical interface in the task force phase at IEEE-SA at the time of this publication. Also, 1/16 of optical lane clock is recommended for TX MCLK and RX MCLK.

- 2. Multi-protocol modules are recommended to adopt the clock rate rate used in Telecom applications.

#### **Optional Transmitter and Receiver Monitor Clock Characteristics**

| Parameter                   | Symbol     | Min | Typical | Max  | Unit | Notes& Conditions         |

|-----------------------------|------------|-----|---------|------|------|---------------------------|

| Impedance                   | Zd         | 80  | 100     | 120  | Q    |                           |

| Frequency                   |            |     |         |      | MHz  | 1/8 of Network lane rate  |

| Output Differential Voltage | $V_{DIFF}$ | 400 |         | 1200 | mV   | Peak to Peak Differential |

| Clock Duty Cycle            |            | 40  |         | 60   | %    |                           |

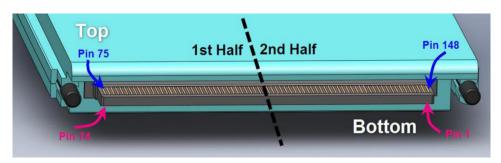

Figure 2. Pad Layout

#### Optical Interconnection Design Innovator

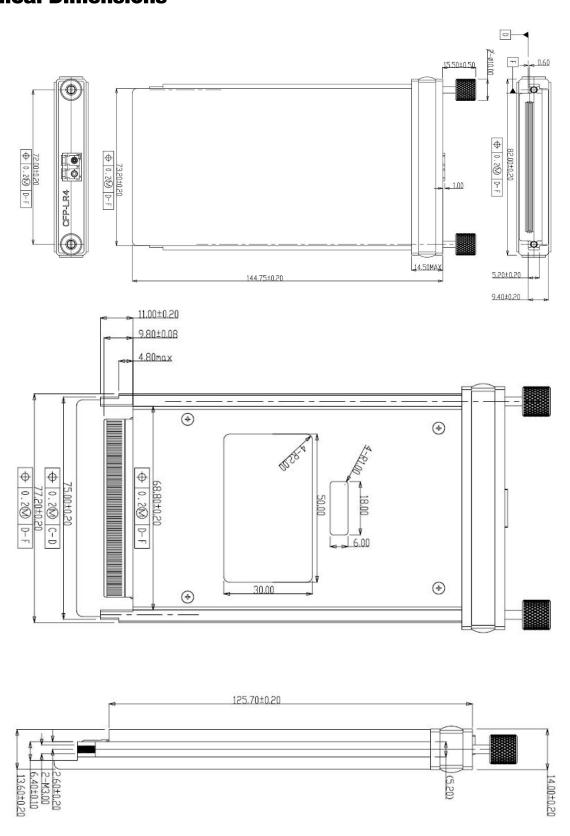

#### **Mechanical Dimensions**

Figure 3. Mechanical Specifications

# **Optical Transceivers Data Sheet**

**Ordering Information**

| Product Description                       | Part Number   |

|-------------------------------------------|---------------|

| CFP LR4, 111.8Gb/s, 1310nm, 10km, SMF, LC | GCF-S101-LR4C |

#### **References:**

- 1. 100GBASE-LR4 100G Ethernet

- 2. OTN OTU4

- 3. CFP MSA

#### **ESD:**

This transceiver is specified as ESD threshold 1kV for SFI pins and 2kV for all other electrical input pins, tested per MIL-STD-883, Method 3015.4 /JESD22-A114-A (HBM). However, normal ESD precautions are still required during the handling of this module. This transceiver is shipped in ESD protective packaging. It should be removed from the packaging and handled only in an ESD protected environment.

#### **Laser Safety:**

This is a Class 1 Laser Product according to IEC 60825-1:2007. This product complies with 21 CFR 1040.10 and 1040.11 except for deviations pursuant to Laser Notice No. 50, dated (June 24, 2007).

#### **Important Notice:**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by GIGALIGHT before they become applicable to any particular order or contract. In accordance with the GIGALIGHT policy of continuous improvement specifications may change without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of GIGALIGHT or others. Further details are available from any GIGALIGHT sales representative.

E-mail: <a href="mailto:sales@gigalight.com">sales@gigalight.com</a>

Official Site :www.gigalight.com

Optical Interconnection Design Innovator

**Revision History**

| Revision | Level       | Date     | Description      |

|----------|-------------|----------|------------------|

| V0       | Preliminary | Feb 2017 | Advance Release. |