# 120G CXP AOC

## Features

- Full duplex 12 channels 850nm parallel active optical cable

- Transmission data rate up to 10.3Gb/s per channel

- Hot pluggable electrical interface

- Differential AC-coupled high speed data interface

- 12 channels 850nm VCSEL array

- ♦ 12 channels PIN photo detector array

- Multi-mode optical fibre cable of up to 300m(OM3) or 400m(OM4)

- Low power consumption < 2.5W

- Operating case temperature 0° C to +70° C

- 3.3V power supply voltage

- ◆ RoHS 6 compliant

## Applications

- Infiniband transmission at 12ch SDR, DDR and QDR

- ♦ Switches, Routers

- ♦ Data Centers

- Other 120G Interconnect Requirement

## Description

CXP-CXP active optic cables are a high performance, low power consumption, long reach interconnect solution supporting 120G Ethernet, fiber channel and PCIe. It is compliant with the 120Gbits Small Form factor Hot-Pluggable CXP-interface. Gigalight CXP AOC is an assembly of 12 full-duplex lanes, where each lane is capable of transmitting data at rates up to 10Gb/s, providing an aggregated rate of 120Gb/s.

Optical Network Transceiver Innovator

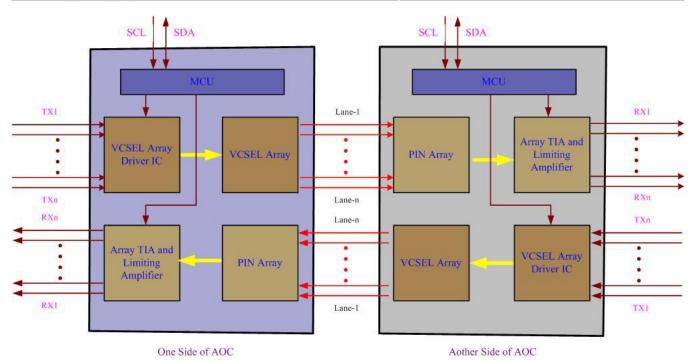

## Figure1. Module Block Diagram

AOC is one kind of parallel transceiver. VCSEL and PIN array package is key technique, through I2C system can contact with module.

## **Absolute Maximum Ratings**

| Parameter                  | Symbol | Min  | Max     | Unit |

|----------------------------|--------|------|---------|------|

| Supply Voltage             | Vcc    | -0.3 | 3.6     | V    |

| Input Voltage              | Vin    | -0.3 | Vcc+0.3 | V    |

| Storage Temperature        | Tst    | -20  | 85      | °C   |

| Case Operating Temperature | Тор    | 0    | 70      | °C   |

| Humidity(non-condensing)   | Rh     | 5    | 95      | %    |

# **Recommended Operating Conditions**

| Parameter                  | Symbol | Min  | Typical | Max  | Unit |

|----------------------------|--------|------|---------|------|------|

| Supply Voltage             | Vcc    | 3.13 | 3.3     | 3.47 | V    |

| Operating Case temperature | Тса    | 0    |         | 70   | °C   |

| Data Rate Per Lane         | fd     | 2.5  |         | 10.3 | Gbps |

Http:// www.gigalight.com.cn

#### Optical Network Transceiver Innovator

| Humidity          | Rh | 5 | 85 | %  |

|-------------------|----|---|----|----|

| Power Dissipation | Pm |   | 2  | W  |

| Fiber Bend Radius | Rb | 3 |    | cm |

## **Specifications**

| Parameter                     | Symbol        | Min     | Typical | Max  | Unit  |

|-------------------------------|---------------|---------|---------|------|-------|

| Differential input impedance  | Zin           | 90      | 100     | 110  | ohm   |

| Differential Output impedance | Zout          | 90      | 100     | 110  | ohm   |

| Differential input voltage    | $\Delta Vin$  | 200     |         | 1200 | mVp-p |

| Differential output voltage   | $\Delta$ Vout | 600     |         | 800  | mVp-p |

| Skew                          | Sw            |         |         | 300  | ps    |

| Bit Error Rate                | BR            |         |         | E-12 |       |

| Input Logic Level High        | VIH           | 2.0     |         | VCC  | V     |

| Input Logic Level Low         | VIL           | 0       |         | 0.8  | V     |

| Output Logic Level High       | VOH           | VCC-0.5 |         | VCC  | V     |

| Output Logic Level Low        | VOL           | 0       |         | 0.4  | V     |

#### Note:

1. BER=10<sup>-12</sup>; PRBS 2<sup>31-1@10.3125Gbps.</sup>

2. Differential input voltage amplitude is measured between TxnP and TxnN

3. Differential output voltage amplitude is measured between RxnP and RxnN

## **Pin Descriptions**

| Pin | Logic | Symbol | Name/Description                    | Ref. |

|-----|-------|--------|-------------------------------------|------|

| A1  |       | GND    | Module Ground                       | 1    |

| A2  | CML-I | Tx1+   | Transmitter non-inverted data input |      |

| A3  | CML-I | Tx1-   | Transmitter inverted data input     |      |

| A4  |       | GND    | Module Ground                       | 1    |

| A5  | CML-I | Tx3+   | Transmitter non-inverted data input |      |

| A6  | CML-I | Tx3-   | Transmitter inverted data input     |      |

| A7  |       | GND    | Module Ground                       | 1    |

| A8  | CML-I | Tx5+   | Transmitter non-inverted data input |      |

| A9  | CML-I | Tx5-   | Transmitter inverted data input     |      |

| A10 |       | GND    | Module Ground                       | 1    |

| A11 | CML-I | Tx7+   | Transmitter non-inverted data input |      |

| A12 | CML-I | Tx7-   | Transmitter inverted data input     |      |

| A13 |       | GND    | Module Ground                       | 1    |

| A14 | CML-I | Tx9+   | Transmitter non-inverted data input |      |

| A15 | CML-I | Tx9-   | Transmitter inverted data input     |      |

Http:// www.gigalight.com.cn

## Optical Network Transceiver Innovator

| A16 |            | GND       | Module Ground                              | 1 |

|-----|------------|-----------|--------------------------------------------|---|

| A17 | CML-I      | Tx11+     | Transmitter non-inverted data input        |   |

| A18 | CML-I      | Tx11-     | Transmitter inverted data input            |   |

| A19 |            | GND       | Module Ground                              | 1 |

| A20 | LVCMOS-I   | SCL       | 2-wire Serial interface clock              | 2 |

| A21 | LVCMOS-I/O | SDA       | 2-wire Serial interface data               | 2 |

| B1  |            | GND       | Module Ground                              | 1 |

| B2  | CML-I      | Tx0+      | Transmitter non-inverted data input        |   |

| B3  | CML-I      | Tx0-      | Transmitter inverted data input            |   |

| B4  |            | GND       | Module Ground                              | 1 |

| B5  | CML-I      | Tx2+      | Transmitter non-inverted data input        |   |

| B6  | CML-I      | Tx2-      | Transmitter inverted data input            |   |

| B7  |            | GND       | Module Ground                              | 1 |

| B8  | CML-I      | Tx4+      | Transmitter non-inverted data input        |   |

| B9  | CML-I      | Tx4-      | Transmitter inverted data input            |   |

| B10 |            | GND       | Module Ground                              | 1 |

| B11 | CML-I      | Tx6+      | Transmitter non-inverted data input        |   |

| B12 | CML-I      | Tx6-      | Transmitter inverted data input            |   |

| B13 |            | GND       | Module Ground                              | 1 |

| B14 | CML-I      | Tx8+      | Transmitter non-inverted data input        |   |

| B15 | CML-I      | Tx8-      | Transmitter inverted data input            |   |

| B16 |            | GND       | Module Ground                              | 1 |

| B17 | CML-I      | Tx10+     | Transmitter non-inverted data input        | 1 |

| B18 | CML-I      | Tx10-     | Transmitter inverted data input            |   |

| B19 |            | GND       | Module Ground                              | 1 |

| B20 |            | VCC3.3-TX | +3.3v Transmitter Power Supply             |   |

| B21 |            | VCC12-TX  | +12v Transmitter Power Supply, Unconnected |   |

| C1  |            | GND       | Module Ground                              | 1 |

| C2  | CML-O      | RX1+      | Receiver non-inverted data output          |   |

| C3  | CML-O      | RX1-      | Receiver inverted data output              |   |

| C4  |            | GND       | Module Ground                              | 1 |

| C5  | CML-O      | RX3+      | Receiver non-inverted data output          |   |

| C6  | CML-O      | RX3-      | Receiver inverted data output              |   |

| C7  |            | GND       | Module Ground                              | 1 |

| C8  | CML-O      | RX5+      | Receiver non-inverted data output          |   |

| C9  | CML-O      | RX5-      | Receiver inverted data output              |   |

| C10 | CITE O     | GND       | Module Ground                              | 1 |

| C10 | CML-O      | RX7+      | Receiver non-inverted data output          |   |

| C12 | CML-O      | RX7-      | Receiver inverted data output              |   |

| C12 |            | GND       | Module Ground                              | 1 |

Http:// www.gigalight.com.cn

### Optical Network Transceiver Innovator

| C14 | CML-O     | RX9+          | Receiver non-inverted data output       |   |

|-----|-----------|---------------|-----------------------------------------|---|

| C15 | CML-O     | RX9-          | Receiver inverted data output           |   |

| C16 |           | GND           | Module Ground                           | 1 |

| C17 | CML-O     | RX11+         | Receiver non-inverted data output       |   |

| C18 | CML-O     | RX11-         | Receiver inverted data output           |   |

| C19 |           | GND           | Module Ground                           | 1 |

| C20 | LVTTL-O   | PRSNT_L       | Module Present, pulled down to GND      |   |

| C21 | LVTTL-I/O | INT_L/Reset_L | Interrupt output, Module Reset          | 2 |

| D1  |           | GND           | Module Ground                           | 1 |

| D2  | CML-O     | RX0+          | Receiver non-inverted data output       |   |

| D3  | CML-O     | RX0-          | Receiver inverted data output           |   |

| D4  |           | GND           | Module Ground                           | 1 |

| D5  | CML-O     | RX2+          | Receiver non-inverted data output       |   |

| D6  | CML-O     | RX2-          | Receiver inverted data output           |   |

| D7  |           | GND           | Module Ground                           | 1 |

| D8  | CML-O     | RX4+          | Receiver non-inverted data output       |   |

| D9  | CML-O     | RX4-          | Receiver inverted data output           |   |

| D10 |           | GND           | Module Ground                           | 1 |

| D11 | CML-O     | RX6+          | Receiver non-inverted data output       |   |

| D12 | CML-O     | RX6-          | Receiver inverted data output           |   |

| D13 |           | GND           | Module Ground                           | 1 |

| D14 | CML-O     | RX8+          | Receiver non-inverted data output       |   |

| D15 | CML-O     | RX8-          | Receiver inverted data output           |   |

| D16 |           | GND           | Module Ground                           | 1 |

| D17 | CML-O     | RX10+         | Receiver non-inverted data output       |   |

| D18 | CML-O     | RX10-         | Receiver inverted data output           |   |

| D19 |           | GND           | Module Ground                           | 1 |

| D20 |           | VCC3.3-RX     | +3.3v Receiver Power Supply             |   |

| D21 |           | VCC12-RX      | +12v Receiver Power Supply, Unconnected |   |

#### Notes:

Module circuit ground is isolated from module chassis ground within the module.

Open collector; should be pulled up with 4.7k – 10k ohms on host board to a voltage between 3.15Vand 3.6V.

Http:// www.gigalight.com.cn

Optical Network Transceiver Innovator

|     |               | Receiver | To   | p Card |          |     |     |

|-----|---------------|----------|------|--------|----------|-----|-----|

| C1  | GND           |          | 1 Г  |        | 56<br>56 | GND | D1  |

| C2  | Rx1p          |          |      |        | Rx0p     |     | D2  |

| C3  | Rx1n          |          |      | t      | Rx0n     |     | D3  |

| C4  | GND           |          |      | с      | 56<br>56 | GND | D4  |

| C5  | Rx3p          |          |      |        | Rx2p     | 3   | D5  |

| C6  | Rx3n          |          |      | Ī      | Rx2n     | 2   | D6  |

| C7  | GND           |          |      |        | 55       | GND | D7  |

| C8  | Rx5p          |          | ge   |        | Rx4p     |     | D8  |

| C9  | Rx5n          |          | Edge |        | Rx4n     | 2   | D9  |

| C10 | GND           |          | Card |        | 55       | GND | D10 |

| C11 | Rx7p          |          | Ca   |        | Rx6p     |     | D11 |

| C12 | Rx7n          |          |      |        | Rx6n     |     | D12 |

| C13 | GND           |          |      |        |          | GND | D13 |

| C14 | Rx9p          |          |      |        | Rx8p     |     | D14 |

| C15 | Rx9n          |          |      | 1      | Rx8n     | 3   | D15 |

| C16 | GND           |          |      |        | 86       | GND | D16 |

| C17 | Rx11p         |          |      |        | Rx10p    | 2   | D17 |

| C18 | Rx11n         |          |      | 1      | Rx10n    | 2   | D18 |

| C19 | GND           |          |      |        |          | GND | D19 |

| C20 | PRSNT_L       |          |      |        | Vcc3.3-F | Rx  | D20 |

| C21 | Int_L/Reset_L |          | IL   |        | Vcc12-R  | х   | D21 |

# Transmitter -- Bottom Card

| A1  | GND   |       | 8 8  |        |        | GND  | B1  |

|-----|-------|-------|------|--------|--------|------|-----|

| A2  | Tx1p  |       |      |        | Tx0p   |      | B2  |

| A3  | Tx1n  | ce Câ |      | а<br>1 | Tx0n   |      | B3  |

| A4  | GND   |       |      |        |        | GND  | B4  |

| A5  | Тх3р  |       |      |        | Tx2p   |      | B5  |

| A6  | Tx3n  |       |      | 6      | Tx2n   |      | B6  |

| A7  | GND   |       |      |        |        | GND  | B7  |

| A8  | Tx5p  |       | ge   |        | Tx4p   |      | B8  |

| A9  | Tx5n  |       | Edge |        | Tx4n   |      | B9  |

| A10 | GND   |       | rd   |        |        | GND  | B10 |

| A11 | Tx7p  |       | Card |        | Tx6p   |      | B11 |

| A12 | Tx7n  |       | 8    |        | Tx6n   |      | B12 |

| A13 | GND   |       |      |        |        | GND  | B13 |

| A14 | Tx9p  |       |      |        | Tx8p   |      | B14 |

| A15 | Tx9n  |       |      | 8      | Tx8n   |      | B15 |

| A16 | GND   |       |      |        |        | GND  | B16 |

| A17 | Tx11p |       |      |        | Tx10p  |      | B17 |

| A18 | Tx11n |       |      |        | Tx10n  |      | B18 |

| A19 | GND   |       |      |        |        | GND  | B19 |

| A20 | SCL   |       |      |        | Vcc3.3 | B-Tx | B20 |

| A21 | SDA   |       |      |        | Vcc12  | -Tx  | B21 |

# Figure2. Electrical Pin-out Details

**PRSNT\_L Pin:** PRSNT\_L is used to indicate when the module is plugged into the host receptacle. It is pulled down to GND through 5.2 kOhm in modules requiring 12V power, and tied directly down to GND in modules requiring 3.3V power only. Gigalight CXP Prsnt\_L Pin internal directly connected to GND and just need single +3.3V Power Supply. The PRSNT\_L signal is asserted "Low" when inserted and deasserted "High" when the module is physically absent from the host connector.

Int\_L/Reset\_L Pin: Int\_L/Reset\_L is a bidirectional signal. When driven from the host, it operates logically as a Reset signal. When driven from the module, it operates logically as an Interrupt signal. In both cases, the signal is asserted low, as indicated by the '\_L' suffix. The Int\_L/Reset\_L signal requires open collector outputs in both the host and module, and must be pulled up on the host board. Int\_L and Reset\_L indications are distinguished from each other by timing - a shorter assertion, driven by the module, indicates an interrupt, and a longer assertion of the signal, driven by the host, indicates a reset.

Int\_L operation: When Int\_L/Reset\_L is pulled "Low" by the module for longer than the minimum interrupt pulse width (tInt\_L,PW-min) and shorter than the maximum interrupt pulse width

Optical Network Transceiver Innovator

(tInt\_L,PW-max) the signal signifies an interrupt. An interrupt indicates a possible module operational fault or a module status critical to the host system. The host identifies the cause of the interrupt using the 2-wire serial interface. Int\_L must operate in pulse mode (vs. static mode), in order to distinguish a short interrupt signal from a longer reset signal, so the module must de-assert Int L/Reset L after the interrupt has been signaled.

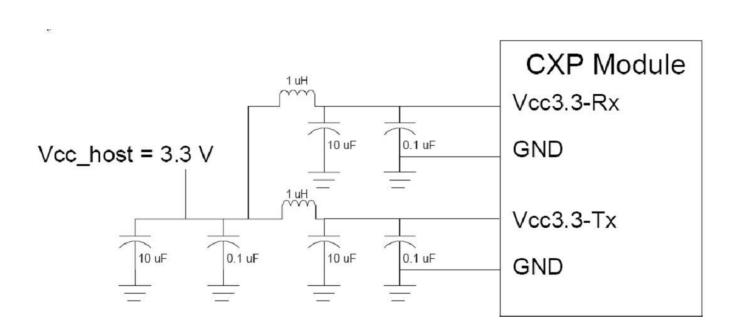

# **Power Supply Filtering**

The host board should use the power supply filtering shown in Figure3.

Figure 3. Host Board Power Supply Filtering

| Timing | for | ${\tt Soft}$ | Control | and | Status | Functions |

|--------|-----|--------------|---------|-----|--------|-----------|

|--------|-----|--------------|---------|-----|--------|-----------|

| Parameter           | Symbol | Max  | Unit | Conditions                                                                                                           |

|---------------------|--------|------|------|----------------------------------------------------------------------------------------------------------------------|

| Initialization Time | t_init | 2000 | ms   | Time from power on <sup>1</sup> , hot plug or rising edge of Reset until the module is fully functional <sup>2</sup> |

Http:// www.gigalight.com.cn

#### Optical Network Transceiver Innovator

| Serial Bus Hardware<br>Ready Time             | t_serial     | 2000 | ms   | Time from power on <sup>1</sup> until module responds to data transmission over the 2-wire serial bus                                                                 |

|-----------------------------------------------|--------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monitor Data Ready<br>Time                    | t_data       | 2000 | ms   | Time from power on <sup>1</sup> to data not ready, bit 0 of Byte 2, deasserted and IntL asserted                                                                      |

| Reset Assert Time                             | t_reset      | 2000 | ms   | Time from rising edge on the ResetL pin until the module is fully functional <sup>2</sup>                                                                             |

| IntL Assert Time                              | ton_IntL     | 200  | ms   | Time from occurrence of condition triggering IntL<br>until Vout:IntL = Vol                                                                                            |

| IntL Deassert Time                            | toff_IntL    | 500  | μs   | Time from clear on read <sup>3</sup> operation of associated<br>flag until Vout:IntL = Voh. This includes deassert<br>times for Rx LOS, Tx Fault and other flag bits. |

| Interrupt Pulse Max<br>Width                  | tintL,PW-max | 50   | μs   | Max Time from falling edge of int_L pin output to<br>rising edge of int_L pin output                                                                                  |

| Rx LOS Assert Time                            | ton_los      | 100  | ms   | Time from Rx LOS state to Rx LOS bit set and IntL asserted                                                                                                            |

| Tx Fault Assert Time                          | ton_Txfault  | 200  | ms   | Time from Tx Fault state to Tx Fault bit set and IntL asserted                                                                                                        |

| Flag Assert Time                              | ton_flag     | 200  | ms   | Time from occurrence of condition triggering flag to associated flag bit set and IntL asserted                                                                        |

| Mask Assert Time                              | ton_mask     | 100  | ms   | Time from mask bit set <sup>4</sup> until associated IntL assertion is inhibited                                                                                      |

| Mask Deassert Time                            | toff_mask    | 100  | ms   | Time from mask bit cleared <sup>4</sup> until associated IntlL operation resumes                                                                                      |

| Power_over-ride or<br>Power-set Assert Time   | ton_Pdown    | 100  | ms   | Time from P_Down bit set <sup>4</sup> until module power<br>consumption enters lower Power Level                                                                      |

| Power_over-ride or<br>Power-set Deassert Time | toff_Pdown   | 300  | ms   | Time from P_Down bit cleared <sup>4</sup> until the module is<br>fully functional3                                                                                    |

| Parameter                                     | Symbol       | Min  | Unit | Conditions                                                                                                                                                            |

| Interrupt Pulse Min<br>Width                  | tintL,PW-min | 5    | μs   | Min Time from falling edge of int_L pin output to<br>rising edge of int_L pin output                                                                                  |

| Reset Pulse Min Width                         | Trst,PW-min  | 25   | ms   | Min Time from falling edge of Reset pin input to rising edge of Reset pin input                                                                                       |

#### Note:

1. Power on is defined as the instant when supply voltages reach and remain at or above the minimum specified value.

2. Fully functional is defined as IntL asserted due to data not ready bit, bit 0 byte 2 deasserted.

3. Measured from falling clock edge after stop bit of read transaction.

4. Measured from falling clock edge after stop bit of write transaction.

# Figure 5. Timing Specifications

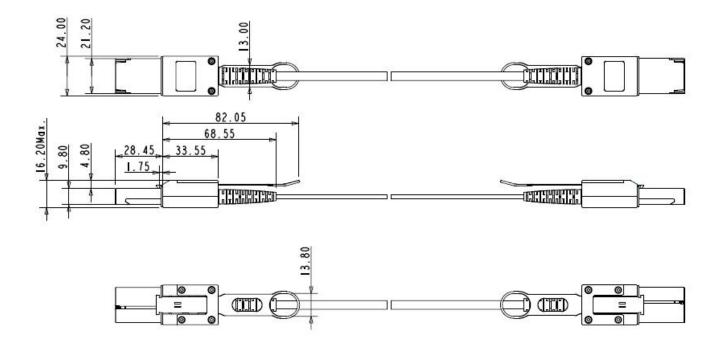

## Mechanical Dimensions

Figure6. Mechanical Specifications

| Ordering information<br>Part Number | n<br>Product Description    |

|-------------------------------------|-----------------------------|

| GCX-MDO121-XXXC                     | XXX=different cable lengths |

|                                     |                             |

| XXX                                 | Cable Length                |

| 003                                 | <b>003</b> =3m              |

| 000 |                  |

|-----|------------------|

| 005 | <b>005</b> =5m   |

| 010 | <b>010</b> =10m  |

| 020 | <b>020</b> =20m  |

| 050 | <b>050</b> =50m  |

| 100 | <b>100</b> =100m |

| 300 | <b>300</b> =300m |

## References

120Gbit/s Small Form-factor Hot-Pluggable CXP-interface

## **Important Notice**

Performance figures, data and any illustrative material provided in this data sheet are typical and must be specifically confirmed in writing by GIGALIGHT before they become applicable to any particular order or contract. In accordance with the GIGALIGHT policy of continuous improvement specifications may change

without notice.

The publication of information in this data sheet does not imply freedom from patent or other protective rights of GIGALIGHT or others. Further details are available from any GIGALIGHT sales representative.

E-mail: <u>sales@gigalight.com.cn</u>

Web : <u>http://www.gigalight.com.cn</u>